# 1 GSPS Quadrature Digital Upconverter with 18-Bit I/Q Data Path and 14-Bit DAC

Data Sheet MCD9957

#### **FEATURES**

1 GSPS internal clock speed (up to 400 MHz analog output) Integrated 1 GSPS 14-bit DAC

250 MSPS input data rate

Phase noise ≤ −124 dBc/Hz (400 MHz carrier at 1 kHz offset)

Excellent dynamic performance >80 dB narrow-band SFDR

8 programmable profiles for shift keying

Sin(x)/(x) correction (inverse sinc filter)

Reference clock multiplier

Internal oscillator for a single crystal operation

Software and hardware controlled power-down

Integrated RAM

Integrated RAM

Phase modulation capability

Multichip synchronization

Easy interface to Blackfin SPORT

Interpolation factors from 4× to 252×

Gain control DAC

Internal divider allows references up to 2 GHz

1.8 V and 3.3 V power supplies

#### **APPLICATIONS**

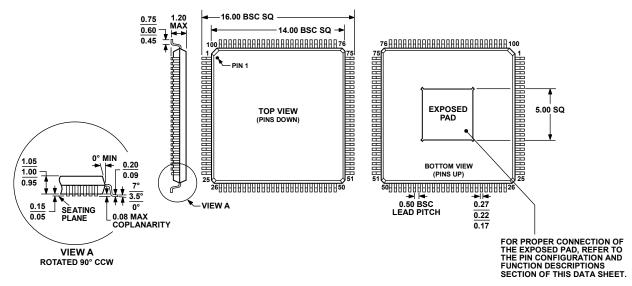

100-lead TQFP\_EP package

HFC data, telephony, and video modems Wireless base station transmissions Broadband communications transmissions Internet telephony

#### **GENERAL DESCRIPTION**

The MCD9957 functions as a universal I/Q modulator and agile upconverter for communications systems where cost, size, power consumption, and dynamic performance are critical. The MCD9957 integrates a high speed, direct digital synthesizer (DDS), a high performance, high speed, 14-bit digital-to-analog converter (DAC), clock multiplier circuitry, digital filters, and other DSP functions onto a single chip. It provides baseband upconversion for data transmission in a wired or wireless communications system.

Unlike its predecessors, it supports a 16-bit serial input mode for I/Q baseband data. The device can alternatively be programmed to operate either as a single tone, sinusoidal source or as an interpolating DAC.

The reference clock input circuitry includes a crystal oscillator, a high speed, divide-by-two input, and a low noise PLL for multiplication of the reference clock frequency.

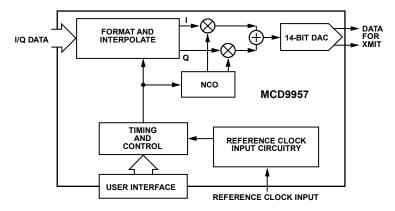

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

# **SPECIFICATIONS**

# **ELECTRICAL SPECIFICATIONS**

AVDD (1.8V) and DVDD (1.8V) = 1.8 V  $\pm$  5%, AVDD (3.3V) = 3.3 V  $\pm$  5%, DVDD\_I/O (3.3V) = 3.3 V  $\pm$  5%, T = 25°C, R<sub>SET</sub> = 10 k $\Omega$ , I<sub>OUT</sub> = 20 mA, external reference clock frequency = 1000 MHz with REFCLK multiplier disabled, unless otherwise noted.

Table 1.

| Parameter                                      | Test Conditions/Comments                 | Min  | Тур  | Max  | Unit   |

|------------------------------------------------|------------------------------------------|------|------|------|--------|

| REF_CLK INPUT CHARACTERISTICS                  |                                          |      |      |      |        |

| Frequency Range                                |                                          |      |      |      |        |

| REFCLK Multiplier                              | Disabled                                 | 60   |      | 1000 | MHz    |

|                                                | Enabled                                  | 3.2  |      | 60   | MHz    |

| Maximum REFCLK Input Divider Frequency         | Full temperature range                   | 1500 | 1900 |      | MHz    |

| Minimum REFCLK Input Divider Frequency         | Full temperature range                   |      | 25   | 35   | MHz    |

| External Crystal                               |                                          |      | 25   |      | MHz    |

| Input Capacitance                              |                                          |      | 3.2  |      | pF     |

| Input Impedance (Differential)                 |                                          |      | 2.9  |      | kΩ     |

| Input Impedance (Single-Ended)                 |                                          |      | 1.45 |      | kΩ     |

| Duty Cycle                                     | REFCLK multiplier disabled               | 45   |      | 55   | %      |

|                                                | REFCLK multiplier enabled                | 40   |      | 60   | %      |

| REF_CLK Input Level                            | Single-ended                             | 50   |      | 1000 | mV p-p |

|                                                | Differential                             | 100  |      | 2000 | mV p-p |

| REFCLK MULTIPLIER VCO GAIN CHARACTERISTICS     |                                          |      |      |      |        |

| VCO Gain (K <sub>V</sub> ) at Center Frequency | VCO0 range setting                       |      | 432  |      | MHz/V  |

|                                                | VCO1 range setting                       |      | 505  |      | MHz/V  |

|                                                | VCO2 range setting                       |      | 560  |      | MHz/V  |

|                                                | VCO3 range setting                       |      | 754  |      | MHz/V  |

|                                                | VCO4 range setting                       |      | 785  |      | MHz/V  |

|                                                | VCO5 range setting <sup>2</sup>          |      | 853  |      | MHz/V  |

| REFCLK_OUT CHARACTERISTICS                     |                                          |      |      |      |        |

| Maximum Capacitive Load                        |                                          |      | 20   |      | pF     |

| Maximum Frequency                              |                                          |      | 25   |      | MHz    |

| DAC OUTPUT CHARACTERISTICS                     |                                          |      |      |      |        |

| Full-Scale Output Current                      |                                          | 8.5  | 20   | 31.5 | mA     |

| Gain Error                                     |                                          | -10  |      | +10  | %FS    |

| Output Offset                                  |                                          |      |      | 3.4  | μΑ     |

| Differential Nonlinearity                      |                                          |      | 0.9  |      | LSB    |

| Integral Nonlinearity                          |                                          |      | 1.7  |      | LSB    |

| Output Capacitance                             |                                          |      | 4.5  |      | pF     |

| Residual Phase Noise                           | At 1 kHz offset, 20 MHz A <sub>OUT</sub> |      |      |      |        |

| REFCLK Multiplier                              | Disabled                                 |      | -150 |      | dBc/Hz |

|                                                | Enabled at 20×                           |      | -141 |      | dBc/Hz |

|                                                | Enabled at 100×                          |      | -139 |      | dBc/Hz |

| AC Voltage Compliance Range                    |                                          | -0.5 |      | +0.5 | V      |

| SPURIOUS-FREE DYNAMIC RANGE (SFDR SINGLE TONE) |                                          |      |      |      |        |

| $f_{OUT} = 20.1 \text{ MHz}$                   |                                          |      | -69  |      | dBc    |

| $f_{OUT} = 98.6 \text{ MHz}$                   |                                          |      | -68  |      | dBc    |

| $f_{OUT} = 201.1 \text{ MHz}$                  |                                          |      | -64  |      | dBc    |

| $f_{OUT} = 397.8 \text{ MHz}$                  |                                          |      | -55  |      | dBc    |

| Parameter                                                     | Test Conditions/Comments                      | Min  | Тур  | Max | Unit                       |

|---------------------------------------------------------------|-----------------------------------------------|------|------|-----|----------------------------|

| NOISE SPECTRAL DENSITY (NSD)                                  |                                               |      |      |     |                            |

| Single Tone                                                   |                                               |      |      |     |                            |

| $f_{OUT} = 20.1 \text{ MHz}$                                  |                                               |      | -166 |     | dBm/Hz                     |

| $f_{OUT} = 98.6 \text{ MHz}$                                  |                                               |      | -160 |     | dBm/Hz                     |

| $f_{OUT} = 201.1 \text{ MHz}$                                 |                                               |      | -155 |     | dBm/Hz                     |

| $f_{OUT} = 397.8 \text{ MHz}$                                 |                                               |      | -150 |     | dBm/Hz                     |

| TWO-TONE INTERMODULATION DISTORTION (IMD)                     | I/Q rate = 62.2 MSPS;<br>16× interpolation    |      |      |     |                            |

| $f_{OUT} = 25 \text{ MHz}$                                    |                                               |      | -81  |     | dBc                        |

| $f_{OUT} = 50 \text{ MHz}$                                    |                                               |      | -76  |     | dBc                        |

| $f_{OUT} = 100 \text{ MHz}$                                   |                                               |      | -71  |     | dBc                        |

| MODULATOR CHARACTERISTICS                                     |                                               |      |      |     |                            |

| Input Data                                                    |                                               |      |      |     |                            |

| Error Vector Magnitude                                        | 2.5 Msymbols/s, QPSK,<br>4× oversampled       |      | 0.58 |     | %                          |

|                                                               | 270.8333 ksymbols/s, GMSK,<br>32× oversampled |      | 0.79 |     | %                          |

|                                                               | 2.5 Msymbols/s, 256-QAM,<br>4× oversampled    |      | 0.38 |     | %                          |

| WCDMA—FDD (TM1), 3.84 MHz Bandwidth,<br>5 MHz Channel Spacing |                                               |      |      |     |                            |

| Adjacent Channel Leakage Ratio (ACLR)                         | IF = 143.88 MHz                               |      | -76  |     | dBc                        |

| Carrier Feedthrough                                           |                                               |      | -77  |     | dBc                        |

| SERIAL PORT TIMING CHARACTERISTICS                            |                                               |      |      |     |                            |

| Maximum SCLK Frequency                                        |                                               |      | 70   |     | Mbps                       |

| Minimum SCLK Pulse Width                                      | Low                                           | 4.5  |      |     | ns                         |

|                                                               | High                                          | 4.5  |      |     | ns                         |

| Maximum SCLK Rise/Fall Time                                   | _                                             |      | 2.2  |     | ns                         |

| Minimum Data Setup Time to SCLK                               |                                               | 6    |      |     | ns                         |

| Minimum Data Hold Time to SCLK                                |                                               | 0    |      |     | ns                         |

| Maximum Data Valid Time in Read Mode                          |                                               |      |      | 11  | ns                         |

| I/O_UPDATE/PROFILE2 to PROFILE 0/RT TIMING CHARACTERISTICS    |                                               |      |      |     |                            |

| Minimum Pulse Width                                           | High                                          | 1    |      |     | SYNC_CLK cycle             |

| Minimum Setup Time to SYNC_CLK                                |                                               | 1.78 |      |     | ns                         |

| Minimum Hold Time to SYNC_CLK                                 |                                               | 0    |      |     | ns                         |

| I/Q INPUT TIMING CHARACTERISTICS                              |                                               |      |      |     |                            |

| Maximum PDCLK Frequency                                       |                                               |      | 250  |     | MHz                        |

| Minimum I/Q Data Setup Time to PDCLK                          |                                               | 1.70 |      |     | ns                         |

| Minimum I/Q Data Hold Time to PDCLK                           |                                               | 0    |      |     | ns                         |

| Minimum TxENABLE Setup Time to PDCLK                          |                                               | 1.70 |      |     | ns                         |

| Minimum TxENABLE Hold Time to PDCLK                           |                                               | 0    |      |     | ns                         |

| MISCELLANEOUS TIMING CHARACTERISTICS                          |                                               |      |      |     | -                          |

| Wake-Up Time <sup>3</sup>                                     |                                               |      | 1    |     |                            |

| Fast Recovery Mode                                            |                                               |      | 8    |     | SYSCLK cycles <sup>4</sup> |

| Full Sleep Mode                                               |                                               |      | -    | 153 | μς                         |

| Minimum Reset Pulse Width High                                |                                               |      | 5    |     | SYSCLK cycles <sup>4</sup> |

| DATA LATENCY (PIPELINE DELAY)                                 |                                               |      | -    |     |                            |

| Data Latency Single Tone Mode                                 |                                               |      |      |     |                            |

| Frequency, Phase and Amplitude-to-DAC output                  | Match delay enable                            |      | 91   |     | SYSCLK cycles <sup>4</sup> |

| Frequency, Phase-to-DAC Output                                | Match delay disabled                          |      | 79   |     | SYSCLK cycles <sup>4</sup> |

| Parameter                               | Test Conditions/Comments | Min  | Тур  | Max  | Unit |

|-----------------------------------------|--------------------------|------|------|------|------|

| SYSCLK CYCLE                            |                          |      |      |      |      |

| Voltage                                 |                          |      |      |      |      |

| Logic 1                                 |                          | 2.0  |      |      | V    |

| Logic 0                                 |                          |      |      | 0.8  | V    |

| Current                                 |                          |      |      |      |      |

| Logic 1                                 |                          |      | 93   | 123  | μΑ   |

| Logic 0                                 |                          |      | 39   | 51   | μΑ   |

| Input Capacitance                       |                          |      | 2.3  |      | pF   |

| XTAL_SEL INPUT                          |                          |      |      |      |      |

| Logic 1 Voltage                         |                          | 1.25 |      |      | V    |

| Logic 0 Voltage                         |                          |      |      | 0.6  | V    |

| Input Capacitance                       |                          | 2.3  |      |      | pF   |

| CMOS LOGIC OUTPUTS                      | 1 mA load                |      |      |      |      |

| Voltage                                 |                          |      |      |      |      |

| Logic 1                                 |                          | 2.8  |      |      | V    |

| Logic 0                                 |                          |      |      | 0.4  | V    |

| POWER SUPPLY CURRENT                    |                          |      |      |      |      |

| DVDD_I/O (3.3V) Pin Current Consumption | QDUC mode                |      | 18   |      | mA   |

| DVDD (1.8V) Pin Current Consumption     | QDUC mode                |      | 615  |      | mA   |

| AVDD (3.3V) Pin Current Consumption     | QDUC mode                |      | 29   |      | mA   |

| AVDD (1.8V) Pin Current Consumption     | QDUC mode                |      | 109  |      | mA   |

| POWER CONSUMPTION                       |                          |      |      |      |      |

| Single Tone Mode                        |                          |      | 810  |      | mW   |

| Continuous Modulation                   | 8× interpolation         |      | 1415 | 1820 | mW   |

| Inverse Sinc Filter Power Consumption   |                          |      | 155  | 208  | mW   |

| Full Sleep Mode                         |                          |      | 15   | 30   | mW   |

$<sup>^{\</sup>rm 1}$  The system clock is limited to 750 MHz maximum in BFI mode.  $^{\rm 2}$  The gain value for VCO range Setting 5 is measured at 1000 MHz.

<sup>&</sup>lt;sup>3</sup> Wake-up time refers to the actual clock frequency used on-chip by the DDS. If the reference clock multiplier is used to multiplier PLL to relock to the reference.

<sup>4</sup> SYSCLK cycle refers to the actual clock frequency used on-chip by the DDS. If the reference clock multiplier is used to multiply the external reference clock frequency, the SYSCLK frequency is the external frequency multiplied by the reference clock multiplication factor. If the reference clock multiplier and divider are not used, the SYSCLK frequency is the same as the external reference clock frequency.

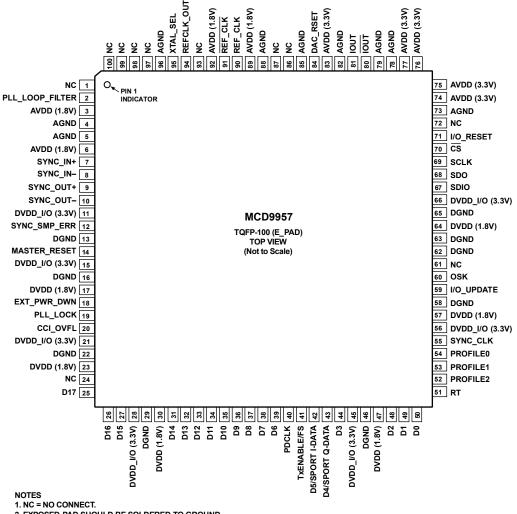

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

2. EXPOSED PAD SHOULD BE SOLDERED TO GROUND.

Figure 2. Pin Configuration

Table 2. Pin Function Descriptions

Pin No. Mnemonic

| Table 2. Pin Function                     |                                    |      |                                                                                                                                                                                                                                                                                                                                 |

|-------------------------------------------|------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No.                                   | Mnemonic                           | I/O¹ | Description                                                                                                                                                                                                                                                                                                                     |

| 1, 24, 61, 72, 86, 87, 93,<br>97 to 100   | NC                                 |      | Not Connected. Allow the device pin to float.                                                                                                                                                                                                                                                                                   |

| 2                                         | PLL_LOOP_FILTER                    | I    | PLL Loop Filter Compensation. See External PLL Loop Filter Components section.                                                                                                                                                                                                                                                  |

| 3, 6, 89, 92                              | AVDD (1.8V)                        | I    | Analog Core VDD. 1.8 V analog supplies.                                                                                                                                                                                                                                                                                         |

| 74 to 77, 83                              | AVDD (3.3V)                        | I    | Analog DAC VDD. 3.3 V analog supplies.                                                                                                                                                                                                                                                                                          |

| 17, 23, 30, 47, 57, 64                    | DVDD (1.8V)                        | I    | Digital Core VDD. 1.8 V digital supplies.                                                                                                                                                                                                                                                                                       |

| 11, 15, 21, 28, 45, 56, 66                | DVDD_I/O (3.3V)                    | I    | Digital Input/Output VDD. 3.3 V digital supplies.                                                                                                                                                                                                                                                                               |

| 4, 5, 73, 78, 79, 82, 85,<br>88, 96       | AGND                               | I    | Analog Ground.                                                                                                                                                                                                                                                                                                                  |

| 13, 16, 22, 29, 46, 58,<br>62, 63, 65     | DGND                               | I    | Digital Ground.                                                                                                                                                                                                                                                                                                                 |

| 7                                         | SYNC_IN+                           | I    | Synchronization Signal, Digital Input (Rising Edge Active). Synchronization signal from external master to synchronize internal subclocks. See the Synchronization of Multiple Devices section.                                                                                                                                 |

| 8                                         | SYNC_IN-                           | I    | Synchronization Signal, Digital Input (Falling Edge Active). Synchronization signal from external master to synchronize internal subclocks. See the Synchronization of Multiple Devices section.                                                                                                                                |

| 9                                         | SYNC_OUT+                          | 0    | Synchronization Signal, Digital Output (Rising Edge Active). Synchronization signal from internal device subclocks to synchronize external slave devices. See the Synchronization of Multiple Devices section.                                                                                                                  |

| 10                                        | SYNC_OUT-                          | 0    | Synchronization Signal, Digital Output (Falling Edge Active). Synchronization signal from internal device subclocks to synchronize external slave devices. See the Synchronization of Multiple Devices section.                                                                                                                 |

| 12                                        | SYNC_SMP_ERR                       | 0    | Synchronization Sample Error, Digital Output (Active High). A high on this pin indicates that the MCD9957 did not receive a valid sync signal on SYNC_IN+/SYNC_IN –. See the Synchronization of Multiple Devices section.                                                                                                       |

| 14                                        | MASTER_RESET                       | 1    | Master Reset, Digital Input (Active High). This pin clears all memory elements and sets registers to default values.                                                                                                                                                                                                            |

| 18                                        | EXT_PWR_DWN                        | I    | External Power-Down, Digital Input (Active High). A high level on this pin initiates the currently programmed power-down mode. See the Power-Down Control section for further details. If unused, tie to ground.                                                                                                                |

| 19                                        | PLL_LOCK                           | 0    | PLL Lock, Digital Output (Active High). A high on this pin indicates that the clock multiplier PLL has acquired lock to the reference clock input.                                                                                                                                                                              |

| 20                                        | CCI_OVFL                           | 0    | CCI Overflow Digital Output, Active High. A high on this pin indicates a CCI filter overflow. This pin remains high until the CCI overflow condition is cleared.                                                                                                                                                                |

| 25 to 27, 31 to 39,<br>42 to 44, 48 to 50 | D[17:0]                            | I/O  | Parallel Data Input Bus (Active High). These pins provide the interleaved, 18-bit, digital, I and Q vectors for the modulator to upconvert. Also used for a GPIO port in Blackfin interface mode.                                                                                                                               |

| 42                                        | SPORT I-DATA                       | 1    | I-Data Serial Input. In Blackfin interface mode, this pin serves as the I-data serial input.                                                                                                                                                                                                                                    |

| 43                                        | SPORT Q-DATA                       | I    | Q-Data Serial Input. In Blackfin interface mode, this pin serves as the Q-data serial input.                                                                                                                                                                                                                                    |

| 40                                        | PDCLK                              | 0    | Parallel Data Clock, Digital Output (Clock). See the Signal Processing section for details.                                                                                                                                                                                                                                     |

| 41                                        | TxENABLE/FS                        | I    | Transmit Enable, Digital Input (Active High). See the Signal Processing section for details. In Blackfin interface mode, this pin serves as the FS input to receive the RFS output signal from the Blackfin.                                                                                                                    |

| 51                                        | RT                                 | I    | RAM Trigger, Digital Input (Active High). This pin provides control for the RAM amplitude scaling function. When this function is engaged, a high sweeps the amplitude from the beginning RAM address to the end. A low sweeps the amplitude from the end RAM address to the beginning. If unused, connect to ground or supply. |

| 52 to 54                                  | PROFILE2,<br>PROFILE1,<br>PROFILE0 | I    | Profile Select Pins, Digital Inputs (Active High). These pins select one of eight phase/frequency profiles for the DDS core (single tone or carrier tone). Changing the state of one of these pins transfers the current contents of all I/O buffers to the corresponding registers. Set up state changes to the SYNC_CLK pin.  |

| 55                                        | SYNC_CLK                           | 0    | Output System Clock/4, Digital Output (Clock). Set up the I/O_UPDATE and PROFILE2/PROFILE1/PROFILE0 pins to the rising edge of this signal.                                                                                                                                                                                     |

| Pin No. | Mnemonic   | I/O¹ | Description                                                                                                                                                                                                                                                                                        |

|---------|------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 59      | I/O_UPDATE | I/O  | Input/Output Update; Digital Input Or Output (Active High), Depending on the Internal I/O Update Active Bit. A high on this pin indicates a transfer of the contents of the I/O buffers to the corresponding internal registers.                                                                   |

| 60      | OSK        | I    | Output Shift Keying, Digital Input (Active High). When using OSK (manual or automatic), this pin controls the OSK function. See the Output Shift Keying (OSK) section of the data sheet for details. When not using OSK, tie this pin high.                                                        |

| 67      | SDIO       | I/O  | Serial Data Input/Output, Digital Input/Output (Active High). This pin can be either unidirectional or bidirectional (default), depending on configuration settings. In bidirectional serial port mode, this pin acts as the serial data input and output. In unidirectional, it is an input only. |

| 68      | SDO        | 0    | Serial Data Output, Digital Output (Active High). This pin is only active in unidirectional serial data mode. In this mode, it functions as the output. In bidirectional mode, this pin is not operational and must be left floating.                                                              |

| 69      | SCLK       | I    | Serial Data Clock. Digital clock (rising edge on write, falling edge on read). This pin provides the serial data clock for the control data path. Write operations to the MCD9957 use the rising edge. Readback operations from the MCD9957 use the falling edge.                                  |

| 70      | <u>CS</u>  | I    | Chip Select, Digital Input (Active Low). Bringing this pin low enables the MCD9957 to detect serial clock rising/falling edges. Bringing this pin high causes the MCD9957 to ignore input on the serial data pins.                                                                                 |

| 71      | I/O_RESET  | ı    | Input/Output Reset. Digital input (active high). This pin can be used when a serial I/O communication cycle fails (see the I/O_RESET—Input/Output Reset section for details). When not used, connect this pin to ground.                                                                           |

| 80      | ĪOUT       | 0    | Open-Source DAC Complementary Output Source. Analog output, current mode. Connect through 50 $\Omega$ to AGND.                                                                                                                                                                                     |

| 81      | IOUT       | 0    | Open-Source DAC Output Source. Analog output, current mode. Connect through 50 $\Omega$ to AGND.                                                                                                                                                                                                   |

| 84      | DAC_RSET   | 0    | Analog Reference Pin. This pin programs the DAC output full-scale reference current. Attach a 10 k $\Omega$ resistor to AGND.                                                                                                                                                                      |

| 90      | REF_CLK    | 1    | Reference Clock Input. Analog input. See the REFCLK Overview section for more details.                                                                                                                                                                                                             |

| 91      | REF_CLK    | 1    | Complementary Reference Clock Input. Analog input. See the REFCLK Overview section for more details.                                                                                                                                                                                               |

| 94      | REFCLK_OUT | 0    | Reference Clock Output. Analog output. See the REFCLK Overview section for more details.                                                                                                                                                                                                           |

| 95      | XTAL_SEL   | I    | Crystal Select (1.8 V Logic). Analog input (active high). Driving the XTAL_SEL pin high enables the internal oscillator to be used with a crystal resonator. If unused, connect it to AGND.                                                                                                        |

|         | EPAD       |      | Exposed Pad (EPAD). The exposed pad should be soldered to ground.                                                                                                                                                                                                                                  |

$<sup>^{1}\,\</sup>text{I}$  is input, O is output, and I/O is for input/output.

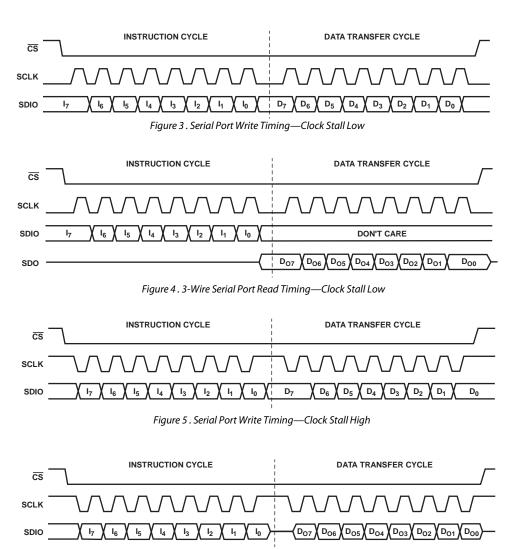

#### **SERIAL I/O TIMING DIAGRAMS**

Figure 3 through Figure 6 provide basic examples of the tim-ing relationships between the various control signals of the serial I/O port.Most Most of the bits in the register map are not transferred to their internal destinations until assertion of an I/O update, which is not included in the timing diagrams that follow.

Figure 6. 2-Wire Serial Port Read Timing—Clock Stall High

# **REGISTER MAP AND BIT DESCRIPTIONS**

# **REGISTER MAP**

Note that the highest number found in the Bit Range column for each register in the following tables is the MSB and the lowest number is the LSB for that register.

**Table 3. Control Registers**

| Register<br>Name<br>(Serial<br>Address)             | Bit<br>Range<br>(Internal<br>Address) | Bit 7<br>(MSB)                          | Bit 6                                   | Bit 5                                  | Bit 4                                                  | Bit 3                             | Bit 2                        | Bit 1              | Bit 0<br>(LSB)             | Default<br>Value |  |  |  |

|-----------------------------------------------------|---------------------------------------|-----------------------------------------|-----------------------------------------|----------------------------------------|--------------------------------------------------------|-----------------------------------|------------------------------|--------------------|----------------------------|------------------|--|--|--|

| Control<br>Function<br>Register 1                   | [31:24]                               | RAM<br>Enable                           | 0                                       | pen                                    | RAM<br>Playback<br>Destination                         | Op                                | en                           | Operatir           | ng Mode                    | 0x00             |  |  |  |

| CFR1<br>(0x00)                                      | [23:16]                               | Manual<br>OSK<br>External<br>Control    | Inverse<br>Sinc Filter<br>Enable        | Clear CCI                              |                                                        | Select<br>DDS<br>Sine<br>Output   | 0x00                         |                    |                            |                  |  |  |  |

|                                                     | [15:8]                                |                                         | pen                                     | Autoclear<br>Phase<br>Accumulator      | Open                                                   | Clear Phase<br>Accumulator        | Load ARR at<br>I/O Update    | OSK<br>Enable      | Select<br>Auto-<br>OSK     | 0x00             |  |  |  |

|                                                     | [7:0]                                 | Digital<br>Power-<br>Down               | DAC Power-<br>Down                      | REFCLK Input<br>Power-Down             | Aux DAC<br>Power-Down                                  | External<br>Power-Down<br>Control | Auto<br>Power-Down<br>Enable | SDIO<br>Input Only | LSB First                  | 0x00             |  |  |  |

| Control<br>Function<br>Register 2<br>CFR2<br>(0x01) | [31:24]                               | Blackfin<br>Interface<br>Mode<br>Active | Blackfin Bit<br>Order                   | Blackfin<br>Early Frame<br>Sync Enable | Open Enable<br>Profile<br>Register<br>as ASF<br>Source |                                   |                              |                    |                            |                  |  |  |  |

|                                                     | [23:16]                               | Internal<br>I/O<br>Update<br>Active     | SYNC_CLK<br>Enable                      |                                        | Open Rear Effe<br>FTW                                  |                                   |                              |                    |                            |                  |  |  |  |

|                                                     | [15:8]                                | I/O Update                              | Rate Control                            | PDCLK Rate<br>Control                  | Data Format                                            | PDCLK<br>Enable                   | PDCLK<br>Invert              | TxENABLE<br>Invert | Q-First<br>Data<br>Pairing | 0x08             |  |  |  |

|                                                     | [7:0]                                 | Open                                    | Data<br>Assembler<br>Hold Last<br>Value | Sync Timing<br>Validation<br>Disable   |                                                        | Open                              |                              |                    |                            |                  |  |  |  |

| Control                                             | [31:24]                               | C                                       | pen                                     | DRV                                    | 0[1:0]                                                 | Open                              | V                            | 'CO SEL[2:0]       |                            | 0x1F             |  |  |  |

| Function                                            | [23:16]                               | C                                       | pen                                     |                                        | I <sub>CP</sub> [2:0]                                  |                                   |                              | Open               |                            | 0x3F             |  |  |  |

| Register 3<br>CFR3<br>(0x02)                        | [15:8]                                | REFCLK<br>Input<br>Divider<br>Bypass    | REFCLK<br>Input<br>Divider<br>ResetB    |                                        |                                                        | Open                              |                              |                    | PLL<br>Enable              | 0x40             |  |  |  |

|                                                     | [7:0]                                 |                                         |                                         |                                        | N[6:0]                                                 |                                   |                              |                    | Open                       | 0x00             |  |  |  |

| Auxiliary                                           | [31:24]                               |                                         |                                         |                                        | Ор                                                     | en                                |                              |                    |                            | 0x00             |  |  |  |

| DAC                                                 | [23:16]                               |                                         |                                         |                                        | Ор                                                     | en                                |                              |                    |                            | 0x00             |  |  |  |

| Control<br>Register                                 | [15:8]                                |                                         |                                         |                                        | Ор                                                     | en                                |                              |                    |                            | 0x7F             |  |  |  |

| (0x03)                                              | [7:0]                                 |                                         |                                         |                                        | FSC                                                    | [7:0]                             |                              |                    |                            | 0x7F             |  |  |  |

| I/O Update                                          | [31:24]                               |                                         | I/O Update Rate[31:24]                  |                                        |                                                        |                                   |                              |                    |                            |                  |  |  |  |

| Rate                                                | [23:16]                               |                                         |                                         |                                        | I/O Update                                             |                                   |                              |                    |                            | 0xFF             |  |  |  |

| Register<br>(0x04)                                  | [15:8]                                |                                         |                                         |                                        | I/O Update                                             | Rate[15:8]                        |                              |                    |                            | 0xFF             |  |  |  |

| (OAO I)                                             | [7:0]                                 |                                         |                                         |                                        | I/O Update                                             | e Rate[7:0]                       |                              |                    |                            | 0xFF             |  |  |  |

Table 4. RAM, ASF, Multichip Sync, and Profile 0 Registers

| Register Name<br>(Serial Address)  | Bit Range<br>(Internal<br>Address) | Bit 7<br>(MSB)                                          | Bit 6                                                  | Bit5     | Bit 4    | Bit 3              | Bit 2                  | Bit 1                         | Bit 0<br>(LSB) | Default<br>Value |  |  |  |  |

|------------------------------------|------------------------------------|---------------------------------------------------------|--------------------------------------------------------|----------|----------|--------------------|------------------------|-------------------------------|----------------|------------------|--|--|--|--|

| RAM Segment                        | [47:40]                            | (11155)                                                 | 5.00                                                   | Ditto    |          | AM Address Ste     |                        | 5.0                           | (200)          | - Turuc          |  |  |  |  |

| Register 0 (0x05)                  | [39:32]                            |                                                         |                                                        |          |          | AM Address St      | •                      |                               |                |                  |  |  |  |  |

|                                    | [31:24]                            |                                                         |                                                        |          |          | RAM End Add        | •                      |                               |                |                  |  |  |  |  |

|                                    | [23:16]                            | RAM Er                                                  | nd                                                     |          |          | TO TOTAL PROPERTY. | Open                   |                               |                |                  |  |  |  |  |

|                                    |                                    |                                                         | Address 0[1:0]                                         |          |          |                    |                        |                               |                |                  |  |  |  |  |

|                                    | [15:8]                             |                                                         | RAM Start Address 0[9:2]                               |          |          |                    |                        |                               |                |                  |  |  |  |  |

|                                    | [7:0]                              | RAM Sta<br>Address 0                                    |                                                        |          | Ор       | en                 | RAM                    | Playback Mode 0[2             | 2:0]           |                  |  |  |  |  |

| RAM Segment                        | [47:40]                            |                                                         |                                                        |          | R/       | AM Address Ste     | ep Rate 1[15:8]        |                               |                |                  |  |  |  |  |

| Register 1 (0x06)                  | [39:32]                            |                                                         | RAM Address Step Rate 1[7:0]                           |          |          |                    |                        |                               |                |                  |  |  |  |  |

|                                    | [31:24]                            |                                                         | RAM End Address 1[9:2]                                 |          |          |                    |                        |                               |                |                  |  |  |  |  |

|                                    | [23:16]                            |                                                         | RAM End Open Address 1[1:0]                            |          |          |                    |                        |                               |                |                  |  |  |  |  |

|                                    | [15:8]                             |                                                         | RAM Start Address 1[9:2]                               |          |          |                    |                        |                               |                |                  |  |  |  |  |

|                                    | [7:0]                              |                                                         | RAM Start Open RAM Playback Mode 1[2:0] Address 1[1:0] |          |          |                    |                        |                               |                |                  |  |  |  |  |

| Amplitude Scale                    | [31:24]                            |                                                         | Amplitude Ramp Rate[15:8]                              |          |          |                    |                        |                               |                |                  |  |  |  |  |

| Factor (ASF)<br>Register<br>(0x09) | [23:16]                            |                                                         |                                                        |          |          | Amplitude Rai      |                        |                               |                | 0x00             |  |  |  |  |

|                                    | [15:8]                             |                                                         |                                                        |          |          | mplitude Scal      | •                      |                               |                | 0x00             |  |  |  |  |

|                                    | [7:0]                              |                                                         |                                                        | Amplitud | de Scale | Factor[5:0]        |                        | Amplitude St                  | ep Size[1:0]   | 0x00             |  |  |  |  |

| Multichip Sync<br>Register (0x0A)  | [31:24]                            | Sync Validation Delay[3:0] Sync Sync Receiver Generator |                                                        |          |          |                    |                        | Sync<br>Generator<br>Polarity | Open           | 0x00             |  |  |  |  |

|                                    | [23:16]                            |                                                         | Enable   Enable   Polarity                             |          |          |                    |                        |                               |                |                  |  |  |  |  |

|                                    | [15:8]                             |                                                         | Sync Generator Delay[4:0] Open                         |          |          |                    |                        |                               |                |                  |  |  |  |  |

|                                    | [7:0]                              |                                                         | Sync Re                                                |          |          |                    |                        | Open                          |                | 0x00<br>0x00     |  |  |  |  |

| Profile 0                          | [63:56]                            | Open                                                    |                                                        | I        | clay[+.c |                    | l<br>Nitude Scale Fact | cude Scale Factor[13:8]       |                |                  |  |  |  |  |

| Register—Single                    | [55:48]                            | Орен                                                    | <u>'</u>                                               | <u> </u> |          | Amplitude Sca      |                        | [01[13.0]                     |                | N/A<br>N/A       |  |  |  |  |

| Tone (0x0E)                        | [47:40]                            |                                                         |                                                        |          | •        | Phase Offset       |                        |                               |                | N/A              |  |  |  |  |

|                                    | [39:32]                            |                                                         |                                                        |          |          | Phase Offset       |                        |                               |                | N/A              |  |  |  |  |

|                                    | [39:32]                            |                                                         |                                                        |          | Er       |                    | g Word[31:24]          |                               |                | N/A              |  |  |  |  |

|                                    | [23:16]                            |                                                         |                                                        |          |          |                    | ig Word[31:24]         |                               |                | N/A              |  |  |  |  |

|                                    | [15:8]                             |                                                         |                                                        |          |          | requency Tunii     |                        |                               |                | N/A<br>N/A       |  |  |  |  |

|                                    | [7:0]                              |                                                         |                                                        |          |          | requency Tuni      |                        |                               |                | N/A              |  |  |  |  |

| Profile 0                          | [63:56]                            |                                                         |                                                        | CCI Inte |          | n Rate[7:2]        | ng word[7.0]           | Spectral Invert               | Inverse        | N/A              |  |  |  |  |

| Register—QDUC<br>(0x0E)            | [55:48]                            |                                                         |                                                        |          |          | Output Sca         | le Factor              |                               | CCI Bypass     | N/A              |  |  |  |  |

|                                    | [47:40]                            |                                                         |                                                        |          |          | Phase Offset       |                        |                               |                | N/A              |  |  |  |  |

|                                    | [39:32]                            |                                                         |                                                        |          |          | Phase Offset       |                        |                               |                | N/A              |  |  |  |  |

|                                    | [31:24]                            |                                                         |                                                        |          | Fr       |                    | ig Word[31:24]         |                               |                | N/A              |  |  |  |  |

|                                    | [23:16]                            |                                                         |                                                        |          |          |                    | ig Word[23:16]         |                               |                | N/A              |  |  |  |  |

|                                    | [15:8]                             |                                                         |                                                        |          |          | requency Tunii     | <u> </u>               |                               |                | N/A              |  |  |  |  |

|                                    | [7:0]                              |                                                         |                                                        |          |          | requency Tuni      |                        |                               |                | N/A              |  |  |  |  |

Table 5. Profile 1, Profile 2, and Profile 3 Registers

| Register<br>Name<br>(Serial | Bit Range<br>(Internal | Bit 7                                                        |                                                                |              |               |                              |               |                    | Bit 0                 | Default      |  |  |  |  |

|-----------------------------|------------------------|--------------------------------------------------------------|----------------------------------------------------------------|--------------|---------------|------------------------------|---------------|--------------------|-----------------------|--------------|--|--|--|--|

| Address)                    | Address)               | (MSB)                                                        | Bit 6                                                          | Bit 5        | Bit 4         | Bit 3                        | Bit 2         | Bit 1              | (LSB)                 | Value<br>N/A |  |  |  |  |

| Profile 1<br>Register—      | [63:56]<br>[55:48]     | U <sub>I</sub>                                               | Open Amplitude Scale Factor[13:8]  Amplitude Scale Factor[7:0] |              |               |                              |               |                    |                       |              |  |  |  |  |

| Single Tone                 | [47:40]                |                                                              |                                                                |              | •             | offset Word[1                |               |                    |                       | N/A<br>N/A   |  |  |  |  |

| (0x0F)                      | [39:32]                |                                                              |                                                                |              |               |                              |               |                    |                       | N/A<br>N/A   |  |  |  |  |

|                             | [31:24]                |                                                              | Phase Offset Word[7:0]  Frequency Tuning Word[31:24]           |              |               |                              |               |                    |                       |              |  |  |  |  |

|                             | [23:16]                |                                                              |                                                                |              |               | Tuning Word                  |               |                    |                       | N/A<br>N/A   |  |  |  |  |

|                             | [15:8]                 |                                                              |                                                                |              |               |                              |               |                    |                       | N/A          |  |  |  |  |

|                             | [7:0]                  |                                                              | Frequency Tuning Word[15:8]  Frequency Tuning Word[7:0]        |              |               |                              |               |                    |                       |              |  |  |  |  |

| Profile 1<br>Register—      | [63:56]                |                                                              |                                                                | CCI Interpol | ation Rate[7: |                              | <u>u[,,o]</u> | Spectral<br>Invert | Inverse CCI<br>Bypass | N/A<br>N/A   |  |  |  |  |

| QDUC (0x0F)                 | [55:48]                |                                                              |                                                                |              | Output        | Scale Factor[                | 7:0]          |                    | - 7/1                 | N/A          |  |  |  |  |

|                             | [47:40]                |                                                              |                                                                |              | •             | offset Word[1                |               |                    |                       | N/A          |  |  |  |  |

|                             | [39:32]                |                                                              |                                                                |              | Phase (       | Offset Word[7                | 7:0]          |                    |                       | N/A          |  |  |  |  |

|                             | [31:24]                |                                                              |                                                                |              | Frequency     | Tuning Word                  | [31:24]       |                    |                       | N/A          |  |  |  |  |

|                             | [23:16]                |                                                              |                                                                |              | Frequency     | requency Tuning Word[23:16]  |               |                    |                       |              |  |  |  |  |

|                             | [15:8]                 |                                                              |                                                                |              | Frequency     | Tuning Word                  | d[15:8]       |                    |                       | N/A          |  |  |  |  |

|                             | [7:0]                  |                                                              |                                                                |              | Frequency     | y Tuning Wor                 | d[7:0]        |                    |                       | N/A          |  |  |  |  |

| Profile 2                   | [63:56]                | O                                                            | pen                                                            |              | -             | Amplitude                    | Scale Facto   | or[13:8]           |                       | N/A          |  |  |  |  |

| Register—                   | [55:48]                |                                                              |                                                                | •            | Amplitud      | e Scale Facto                | r[7:0]        |                    |                       | N/A          |  |  |  |  |

| Single Tone<br>(0x10)       | [47:40]                |                                                              |                                                                |              | Phase C       | Offset Word[1                | 5:8]          |                    |                       | N/A          |  |  |  |  |

| (0.00)                      | [39:32]                |                                                              |                                                                |              | Phase (       | Offset Word[7                | 7:0]          |                    |                       | N/A          |  |  |  |  |

|                             | [31:24]                |                                                              |                                                                |              | Frequency     | Tuning Word                  | l[31:24]      |                    |                       | N/A          |  |  |  |  |

|                             | [23:16]                |                                                              |                                                                |              | Frequency     | Tuning Word                  | l[23:16]      |                    |                       | N/A          |  |  |  |  |

|                             | [15:8]                 |                                                              |                                                                |              | Frequency     | Tuning Wor                   | d[15:8]       |                    |                       | N/A          |  |  |  |  |

|                             | [7:0]                  |                                                              | Frequency Tuning Word[7:0]                                     |              |               |                              |               |                    |                       |              |  |  |  |  |

| Profile 2<br>Register—      | [63:56]                | CCI Interpolation Rate[7:2] Spectral Inverse CCI Inverse CCI |                                                                |              |               |                              |               |                    | N/A                   |              |  |  |  |  |

| QDUC (0x10)                 | [55:48]                |                                                              |                                                                |              | •             | Scale Factor[                |               |                    |                       | N/A          |  |  |  |  |

|                             | [47:40]                |                                                              |                                                                |              |               | offset Word[1                |               |                    |                       | N/A          |  |  |  |  |

|                             | [39:32]                |                                                              |                                                                |              |               | Offset Word[7                |               |                    |                       | N/A          |  |  |  |  |

|                             | [31:24]                |                                                              |                                                                |              | ' '           | Tuning Word                  |               |                    |                       | N/A          |  |  |  |  |

|                             | [23:16]                |                                                              |                                                                |              |               | Tuning Word                  |               |                    |                       | N/A          |  |  |  |  |

|                             | [15:8]                 |                                                              |                                                                |              | <u>·</u>      | Tuning Word                  |               |                    |                       | N/A          |  |  |  |  |

|                             | [7:0]                  |                                                              |                                                                |              | Frequency     | y Tuning Wor                 |               |                    |                       | N/A          |  |  |  |  |

| Profile 3<br>Register—      | [63:56]                | 0                                                            | pen                                                            |              | Δ 10.         | •                            | Scale Facto   | or[13:8]           |                       | N/A          |  |  |  |  |

| Single Tone                 | [55:48]                |                                                              |                                                                |              |               | e Scale Facto                |               |                    |                       | N/A          |  |  |  |  |

| (0x11)                      | [47:40]                |                                                              |                                                                |              |               | Offset Word[1                |               |                    |                       | N/A          |  |  |  |  |

|                             | [39:32]                |                                                              |                                                                |              |               | Offset Word[7<br>Tuning Word |               |                    |                       | N/A          |  |  |  |  |

|                             | [31:24]                |                                                              |                                                                |              |               |                              |               |                    |                       | N/A          |  |  |  |  |

|                             | [23:16]<br>[15:8]      |                                                              |                                                                |              |               | Tuning Word Tuning Word      |               |                    |                       | N/A          |  |  |  |  |

|                             | [7:0]                  |                                                              |                                                                |              |               | Tuning Work                  |               |                    |                       | N/A<br>N/A   |  |  |  |  |

| Profile 3<br>Register—      | [63:56]                |                                                              |                                                                | CCI Interpol | ation Rate[7: |                              | <u>u[7.0]</u> | Spectral<br>Invert | Inverse CCI<br>Bypass | N/A          |  |  |  |  |

| QDUC                        | [55:48]                |                                                              |                                                                |              | Output        | Scale Factor[                | 7:0]          |                    | 1 -7135               | N/A          |  |  |  |  |

| (0x11)                      | [47:40]                |                                                              |                                                                |              |               | Offset Word[1                |               |                    |                       | N/A          |  |  |  |  |

|                             | [39:32]                |                                                              |                                                                |              |               | Offset Word[7                |               |                    |                       | N/A          |  |  |  |  |

|                             | [31:24]                |                                                              |                                                                |              |               | Tuning Word                  |               |                    |                       | N/A          |  |  |  |  |

|                             | [23:16]                |                                                              |                                                                |              |               | Tuning Word                  |               |                    |                       | N/A          |  |  |  |  |

|                             | [15:8]                 |                                                              |                                                                |              |               | Tuning Word                  |               |                    |                       | N/A          |  |  |  |  |

|                             | [7:0]                  |                                                              |                                                                |              |               | y Tuning Wor                 |               |                    |                       | N/A          |  |  |  |  |

Table 6. Profile 4, Profile 5, and Profile 6 Registers

| Register<br>Name<br>(Serial<br>Address) | Bit<br>Range<br>(Internal<br>Address) | Bit 7 (MSB)             | Bit 6                                                          | Bit 5     | Bit 4     | Bit 3     | Bit 2     | Bit 1                | Bit 0 (LSB)        | Default<br>Value |  |  |  |

|-----------------------------------------|---------------------------------------|-------------------------|----------------------------------------------------------------|-----------|-----------|-----------|-----------|----------------------|--------------------|------------------|--|--|--|

| Profile 4                               | [63:56]                               | Open                    | •                                                              |           | •         | Α         | mplitude  | e Scale Factor[13:8] |                    | N/A              |  |  |  |

| Register—                               | [55:48]                               |                         |                                                                |           | Amp       | olitude S | ale Fact  | or[7:0]              |                    | N/A              |  |  |  |

| Single Tone<br>(0x12)                   | [47:40]                               |                         |                                                                |           | Ph        | ase Offse | et Word[´ | 15:8]                |                    | N/A              |  |  |  |

| (UX12)                                  | [39:32]                               |                         | Phase Offset Word[7:0]                                         |           |           |           |           |                      |                    |                  |  |  |  |

|                                         | [31:24]                               |                         | Frequency Tuning Word[31:24]                                   |           |           |           |           |                      |                    |                  |  |  |  |